# DESIGN OF SECOND ORDER BUTTERWORTH HIGHPASS FILTER USING CMOS TECHNOLOGY

### Anggraini Puspita Sari, Agung Darmawansyah, M. Julius St.

Abstract-The research Complementary Metal-Oxide Semiconductor (CMOS) Technology for Design of second order butterworth highpass filter IC. This is caused CMOS have excellence low power dissipation and small size. This research aims to know performance, quality and reliability second order butterworth highpass filter circuit. The method used to problem solving, analysis with the literature and the simulation use pspice program for exam the specification of circuit. To make IC picture using DSCH software and layout circuit using Microwind program. From examination result -2,99dB for gain voltage parameter, frequency -40dB and 88,25° phase shift second order highpass filter. The result of this circuit have low power dissipation although applied to second order highpass filter equal 2,28mW better than generality IC second order highpass filter (GH580). Wide of layout circuit is 1110µm x 385µm.

Index Terms— highpass filter, butterworth filter, CMOS Technology.

#### I. INTRODUCTION

In the recent years, semiconductor technology especially integrated circuit is the best choice to minimize the dimensions of a device. Considering the flexibility, low power requirements, and low cost, the incorporation of electronic components such as resistors, capacitors, transistors, diodes and other integrated circuit components allows for the creation of flexible and resilient chip designs. The technology applied to minimize the size of integrated circuit components is microelectronics technology. This technology is applied to realize the manufacture of small dimensional electronic circuits with consideration of increasing the capability of each component, weight reduction, strength of test power and the ability of stability to the environment.[1] [2][3]

During this time, the evolution of CMOS technology more utilized in digital circuit but not so far for analog

Aggraini Puspita Sari, Electrical Engineering Department of Universitas Merdeka Malang, Malang, Indonesia (085895241585; email anggraini.puspita@unmer.ac.id)

Agung Darmawansyah, Electrical Engineering Department of Universitas Brawijaya, Malang, Indonesia (email agung.darmawansyah@ub.ac.id)

M. Julius St., Electrical Engineering Department of Universitas Brawijaya, Malang, Indonesia (08989719023; email m.julius.st@ub.ac.id) circuit. So in this research could explore for CMOS technology in analog circuit.[4]

In the field of analog electronics, filters are often used to reduce noise. One type of filter used is a highpass filter. The highpass filter passes all signal frequencies above the cut-off frequency and weakens all signals whose frequency is below the cut-off frequency. When designing a circuit requires a fast design technique and optimal layout to get the smallest possible size. In this research, we chose the layout of second order Butterworth filter IC using CMOS technology because it has advantages in low power dissipation and the size is very small. Power dissipation greatly affects workability, reliability, packaging, cost and brevity [1]. The type of Butterworth filter is selected to produce a maximal flat response on the passband portion.

#### II. REASERCH METODS

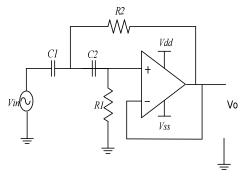

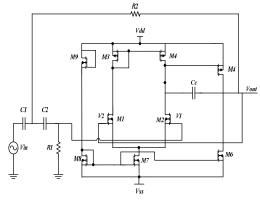

In this research will be designed a highpass filter with CMOS transistor. Fig. 1 shows the second order highpass filter circuit.

#### Fig. 1 The Second Order Highpass Filter Circuit

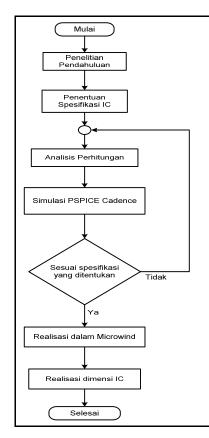

The operational amplifier (op-amp) used in this research is a second order op-amp CMOS with low power dissipation. Low power dissipation affects performance, reliability, packaging, cost, portability. This op-amp circuit consists of nine CMOS transistors and capacitors. The op-amp used in this research is a second order opamp CMOS with low power dissipation. Low power dissipation affects performance, reliability, packaging, cost, portability. This opamp circuit consists of nine CMOS transistors and a capacitor. The calculation of the values of each transistor is generated from the current analysis. The flowchart of design IC are shown Fig. 2

Fig. 2 The Flowchart Of Design IC

#### III. CALCULATION RESULT OF HIGHPASS BUTTERWORTH FILTER IC

Before determining transistor comparison, the previously determined specifications CMOS operational amplifier second order is as follows: Gain Bandwidth (GB) = 2MHz, I<sub>7</sub>= 25 $\mu$ A, V<sub>DD</sub>=5V, V<sub>SS</sub>= -5V,  $\lambda_P$  = 0,02V<sup>-1</sup>,  $\lambda_N$ = 0,01V<sup>-1</sup>, V<sub>TN</sub>= 0,8V, V<sub>TP</sub>= -0,8V, K<sub>N</sub>=10 $\mu$ A/V<sup>2</sup>, K<sub>P</sub>= 4 $\mu$ A/V<sup>2</sup>, C<sub>L</sub>= 5pF, V<sub>in (maks)</sub>= 3,5 V,V<sub>in (min)</sub>= -2,5V, R<sub>in</sub>= ~.[2]

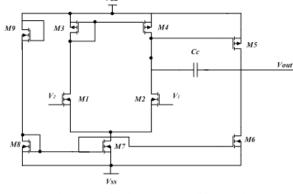

Fig. 3 shows a second order CMOS amplifier circuitada

Fig. 3 Second Order CMOS Amplifier Circuit

The design procedure begins by calculating the value of the compensation capacitor (Cc). To obtain the comparison of gmi and gm5 values based on the comparison of frequency amplification values of  $3\omega 0$  to obtain a ratio of 1/3.

$$Cc = 3 \cdot C_{L} \frac{g_{mi}}{g_{m5}}$$

$$Cc = 3 \cdot 5 \cdot \frac{1}{3} = 5 \text{ pF}$$

Then determined the minimum value of current I7 =  $25 \mu A$ . Based on the specification of I7 and the compensation capacitor calculation results obtained slew rate (SR).

$$I_7 = SR \cdot Cc$$

25.10<sup>-6</sup> = SR × 5.10<sup>-12</sup>

SR = 5 V/ $\mu$  s

In design using microwind with 0.8  $\mu$ m CMOS Process. [2][3]Based on the calculations that have been done then the size of all transistors are:

- L1 = L2 = 0,8 μm W1 = W2 = 15,8.0,8 = 12,6μm

- L3 =L4 = 0,8 µm W3 = W4 = 2,78.0,8 = 2,2µm

- $L5 = 0.8 \ \mu m$

- $W5 = 31, 3..0, 8 = 25 \mu m$

- L6 = 0,8 μm W6 = 18.0,8 = 14,4μm

- $L7 = L8 = 0.8 \ \mu m$ W7 = W8 = 3.0,8 = 2,4 $\mu m$

- W9 = 0.8 µm

$$L9 = \frac{0.8.10^{-6}}{0.1} = 8\mu m$$

The value of power dissipation is:

$$\begin{split} DP &= (I_5 + I_7 + I_8) . (V_{DD} - V_{SS}) \\ &= (150.10^{-6} + 25.10^{-6} + 25.10^{-6}) . (5 + 5) \\ &= 2 \ mW \\ The calculation of low frequency gain is : \end{split}$$

$$A_d = 20\log \frac{2.g_{m2}g_{m5}}{(\lambda_P + \lambda_N)I_5(\lambda_P + \lambda_N)I_7}$$

$$= 20 \log \frac{2.6,28.10^{-5}.1,88.10^{-4}}{0,03.0,15.10^{-3}.0,03.25.10^{-6}}$$

= 20 log 6996,38

= 76,9 dB

The calculation of CMRR is:

$$CMRR = 20 \log \frac{2 \cdot g_{m2} g_{m3}}{\lambda_P \lambda_N I_3 I_7}$$

= 20 \log \frac{2.62, 8.10^{-6} \cdot 1, 67.10^{-5}}{0, 02.0, 01.12, 5.10^{-6} \cdot 25.10^{-6}}

= 20 \log 33560

= 90,5 \dB

In low frequencies, noise is caused by the bias currents and the asymmetry of components. In high frequencies, the noise is amplified again by the capacitance contained in the component, theoretically Ap = 1, then:

$$PSRR = 20 \log \frac{A_d}{A_p}$$

$$= 20 \log 6996,38$$

The value of the output voltage range can be calculated are :

$$\begin{split} V_{out(min)} &= V_{SS} + (V_{GS6} - V_{T6}) \\ &= -5 + 1,3 \\ &= -3,7V \\ V_{out(max)} &= V_{DD} - (V_{SG5} - V_T) \\ &= 5 - 1,5 \\ &= 3,5 \ V. \end{split}$$

## IV. SIMULATION RESULT

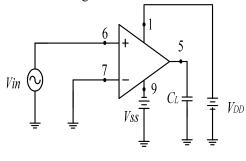

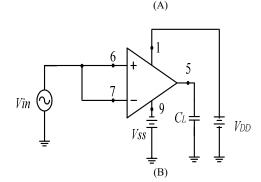

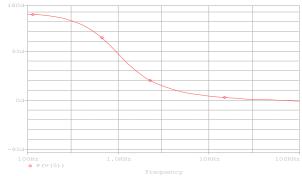

Second order highpass IC circuit simulation of differential mode gain configuration and common mode are shown in Fig. 4.

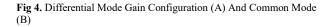

The total power dissipation of the second order CMOS amplifier is 2.28 mW. Strengthening the voltage, the ratio between the output voltage at point 5 to the input voltage at point 6 is 8985.2V shown in Fig. 5, so:

$Ad (dB) = 20 \log \frac{Vout}{Vin}$  $= 20 \log 8985,2$

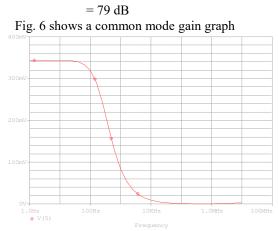

Based on the analysis of common mode gain, the ratio between the output voltage at point 5 to the input voltage at point 6 is 0.34403V so:

Ac (dB) = 20 log

$$\frac{Vout}{Vin}$$

= 20 log 0,34403

= -9,2 dB

The value of CMRR is:

$$CMRR = 20 \log \frac{Ad}{Ac}$$

$$= Ad (dB) - Ac (dB)$$

$$= 79 - (-9,2)$$

$$= 88,2dB$$

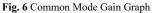

The circuitsimulation of PSRR positive (PSRR<sup>+</sup>) and PSRR negative (PSRR<sup>-</sup>) are shown in Fig.7.

(B) Fig.7 The Circuit Simulation of  $PSRR^+$  and  $PSRR^-$

Fig. 8 The Simulation Result of PSRR<sup>+</sup>Graph

Fig. 8 shows a the result of comparison of the output voltage at point 5 to the  $V_{DP}$  voltage at point 10 is 513.504V, then:

Fig. 9 The Simulation Result of PSRR Graph

Fig.9 shows a the result of comparison of the output voltage at point 5 to the  $V_{DP}$  voltage at point 11 is 570.992mV, then:

$$Ap^{-} (dB) = 20 \log \frac{Vout}{V_{DP}}$$

= 20 log 0,570992

= -4,8 dB

So, the value of PSRR<sup>-</sup>is:

PSRR<sup>-</sup> = Ad (dB) - Ap<sup>-</sup> (dB)

= 79 - (-4,8)

= 83,8 dB

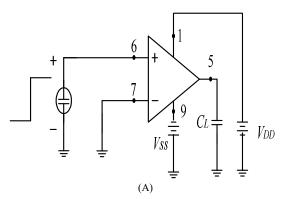

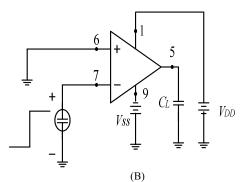

The circuit simulation of slew rate positive  $(SR^+)$  and slew rate negative  $(SR^-)$  are shown in Fig. 10.

Fig. 10 The Circuit Simulation of SR<sup>+</sup> and SR<sup>-</sup>

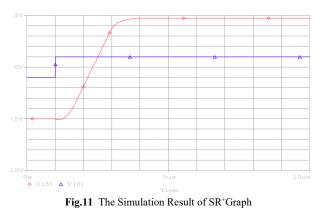

The Simulation Result of SR<sup>+</sup> Graph are shown Fig.11 and the value of SR<sup>+</sup>is:

$$SR^{+} = \frac{Vmaks - V\min}{\Delta t}$$

$$= \frac{4,7493 - (-5)}{3,913.10^{-6} - 1.10^{-6}}$$

$$= 3,35 \text{ V/}\mu\text{s}$$

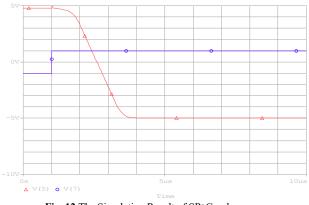

Fig. 12 The Simulation Result of SR  $\mbox{\rm Graph}$

Fig. 12 shows a The Simulation Result of SR<sup>-</sup> Graph and the value of SR<sup>-</sup> is:

$$SR^{-} = \frac{Vmaks - V\min}{\Delta t}$$

$$= \frac{-4,9676 - 4,7967}{3,9826 \cdot 10^{-6} - 1.10^{-6}}$$

$$= -3.27 \text{ V/us}$$

The second order highpass filter circuit are shown in Fig. 13.

Fig.13 The Second Order Highpass Filter Circuit

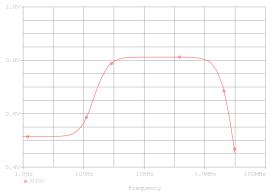

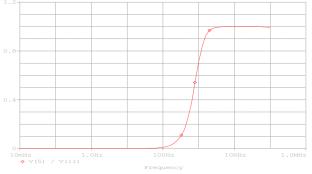

Fig. 14 Graph of Frequency Response of Second Order Highpass Filter at fo = 1kHz

Fig. 14 shows a Graph of Frequency Response of Second Order Highpass Filter when fo = 1kHz.Atfo = 1kHz, the voltage gain (A<sub>0</sub>) is equal to 0.709 V.

Fig. 15shows athe graph of response frequency highpass filter (in dB) at fo = 1 kHz. Pada saat fo = 1 kHz penguatan tegangan Ao sama dengan -2,99dB.

Fig. 15The Graph of Response Frequency Highpass Filter (in dB) at fo = 1 kHz

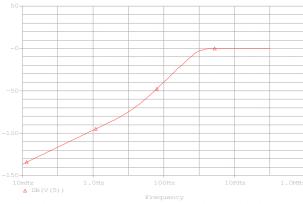

Fig. 16The Graph of Second Order Highpass Filter Phase At fo = 1kHz

Fig.16shows the magnitude of the gain (in dB), which occurs at fo is -2.99 dB with a phase angle of 88.25°.

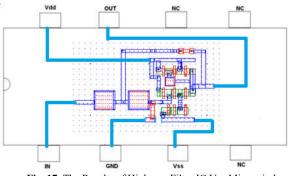

Fig.17 shows the results of highpass filter IC use Microwind. The IC area is  $1110\mu m x 385\mu m$ .

Fig. 17 The Results of Highpass Filter IC Use Microwind

Table 1 shows a Calculation and Simulation Result to Second Order Op-amp CMOS and Table 2 shows a Result of Design IC and IC GH580.

| Table1.Calculation and Simulation Result to Second |

|----------------------------------------------------|

| Order Op-amp CMOS                                  |

| Parameter | Calculation      | Simulation         |

|-----------|------------------|--------------------|

|           | Results          | Results            |

| Ad        | 76,9 dB          | 79dB               |

| SR        | 5 V/µs           | 3,35V/µs           |

| CMRR      | 90,5 dB          | 88,2dB             |

| PSRR      | 76,9 dB          | 84,8dB             |

| PD        | 2 mW             | 2,28mW             |

| Vo        | -3,7 V s/d 3,5 V | -5V s/d<br>4,7542V |

| Parameter | Design      | IC          |

|-----------|-------------|-------------|

|           | Results     | GH580       |

| Туре      | Highpass    | Highpass    |

| Order     | Dua         | Dua         |

| Туре      | Butterworth | Butterworth |

| PD        | 2,28mW      | 25mW        |

| PSRR      | 83,8dB      | 56dB        |

## V. CONCLUTION

The conclusion of this research are input signal given in highpass filter circuit above cutoff frequency will be passed while below cutoff frequency will be damped, design result for CMOS amplifier and second order highpass filter can be fabricated due to shift of cutoff frequency and voltage gain close to expected that is for frequency cutoff = 1kHz and voltage gain (Ao) = 0.707V or -3dB, the design excellence IC is having a small power dissipation value of 2.28mW compared to the second order IC GH580, the results of design second order highpass IC use Microwind have IC area is 1110 $\mu$ m x 385 $\mu$ m.

#### REFERENCES

- Amm Y. Taur, CMOS design near the limit of scaling, IBM J. Res. & Dev. Vol. 46, No. 2/3, pp. 213-222, 2002.

- [2] Geiger, Randall L., Allen, Phillip E., Strader, Noel R. 1990. VLSI Design Techniques For Analog and Digital Circuits. McGraw-Hill. Singapore.

- [3] Rashid, Muh. 1999. Microelectronic Circuits Analysis and Design. PWS Publishing Company. Boston.

- [4] Bram Nauta and Anne-Johan Annema. Analog/RF circuit design techniques for nanometerscale IC technologies. 2005. Proceedings of ESSCIRC, Grenoble, France. 0-7803-9205-1/05.